the following is the technique should apply for minimizing the clock skew:

Buffering the clock:

In a large system, the single clock signal may not have adequate fanout to drive all of the devices, so it may be necessary to provide one or two copies of the clock signal.

The buffering method of figure1 produces excessive clock skew,

since CLOCK1 and CLOCK2 are delayed through an extra buffer compared to CLOCK

port of the destination register sonner than the

source register, so, the destination register will

clock in the source register ( current) value before the source register receives it's clock edge.

Buffering the clock:

In a large system, the single clock signal may not have adequate fanout to drive all of the devices, so it may be necessary to provide one or two copies of the clock signal.

|

| Figure 1 |

The buffering method of figure1 produces excessive clock skew,

since CLOCK1 and CLOCK2 are delayed through an extra buffer compared to CLOCK

|

| Figure 2 |

A recommended method is shown in figure 2.

all of the clock signals go through identical buffers and thus have roughly equal delays

Add delay in Data path:

|

| Figure 3 |

The amount of the inserted delay

(number of buffer and invters) in the data path should be large enough so that the delay becomes sufficiently greater than the clock skew.

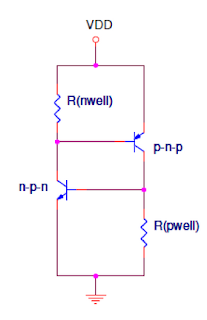

Clock Reversing:

In this method, the clock signal arrives at the clock

|

| Figure 4 |

source register, so, the destination register will

clock in the source register ( current) value before the source register receives it's clock edge.

Alternate Phase Clocking:

the following are the most common methods of alternate phase clocking

In this method, the sequentially adjacent registers are clocked on opposite edges of the clock

this method provides a short path-clock skew margin of about one-half clock cycle.

In this method, the sequentially adjacent registers are alternatively clocked on two different registers,

there is a safety margin approximately equal to the phase difference of the two phases

the following are the most common methods of alternate phase clocking

- clocking on alternate edges

In this method, the sequentially adjacent registers are clocked on opposite edges of the clock

this method provides a short path-clock skew margin of about one-half clock cycle.

- clocking with two phases

In this method, the sequentially adjacent registers are alternatively clocked on two different registers,

there is a safety margin approximately equal to the phase difference of the two phases