- A virtual clock can be defined as a clock without any source or in other words a virtual clock is a clock that has been defined, but has not been associated with any pin/port.

- It does not physically exist in the design but it does exist in the memory. It is used as a reference to constrain the interface pins by relating the arrivals at input/output ports.

We can simply define the virtual clock by the create_clock command but we don’t need to give any generation point since for virtual clock there is no actual clock source in the design,

create_clock -name VIR_CLK -period 10 -waveform {0 5}

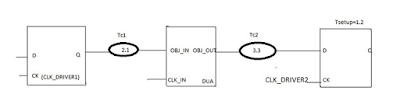

An example where virtual clock is applicable is shown below-

The design under analysis gets its clock from CLK_IN but the clock driving input port OBJECT_IN is CLK_DRIVER1.How are we supposed to specify the IO constraint on input port OBJECT_IN in such cases? Output port OBJCET_OUT faces the same issue.

To handle such cases, a virtual clock can be defined with no specification of the source port/pin

the source port/pin

create_clock -name VIR_CLK_DRIVER1 -period 10 -waveform {2 8}create_clock -name VIR_CLK_DRIVER2 -period 8 -waveform {0 4}

Now, the IO constraints can be specified relative to this virtual clock

set_input_delay -clock VIR_CLK_DRIVER1 -max 2.7 / [get_ports OBJ_IN]

set_input_delay -clock VIR_CLK_DRIVER2 -max 4.5 / [get_ports OBJ_OUT]

The figure 2 shows the timing relationships on the input path. This constrains the input path in the design under analysis to be 5.3ns or less.

개새키야

ReplyDelete느금마

ReplyDeletehttps://youtu.be/sv2X-lALMoo - virtual detail understanding go for this video

ReplyDeleteThanks for sharing great informational content. micro usb to hdmi write for us + travel

ReplyDeleteVLSI Interview Questions and Answers

ReplyDelete