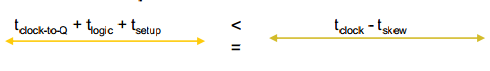

Sequential Circuit Timing

This section covers several timing considerations encountered in the design of synchronous sequential circuits

Why setup time and hold time arise in a flip flop?

To understand why setup and hold time arises in a flip-flop one needs to begin by looking at its basic function.

These flip-flop building blocks include inverters and transmission gates.

Fig: Inveter diagram

Inverters are used to invert the input

Fig: Transmission gate (Tx)

It is a parallel connection of nMOS and pMOS with complementary inputs to both MOSFETs

It is Bidirectional, it carries current in either direction. Depending on the voltage on the gate, the connection between the input and output is either low-resistance or high-resistance, so that Ron = 100 Ω or less and

Roff > 5 MΩ. This effectively isolates the output from the input.

The transistor level structure of a D flip-flop contains two 'back-to-back' inverters known as a 'latching circuit,' since it retains a logic value. Immediately after the D input, an inverter may or may not be present (see figure)

Fig : The transistor level structure of D flip-flop contains two back-to-back inverters known as a'latching circuit.

It is a positive edge triggered flip flop because output arrives at the positive edge of clk

When clk = 0 , if D changes, the change would reflect only at node z

When clk = 1, it would appear at the output only

Here, setup and hold time came into picture

Lets refresh what is setup and hold time?

Setup time: it is defined as the minimum amount of time before the clock's active edge that data must be stable for it to be latched correctly.

Hold time: it is defined as the minimum amount of time after the clock's active edge during which data must be stable.

Here, setup and hold time is measured with respect to the active clock edge only.

why setup time came into picture?

see the following fig carefully

Fig: node D to Z delay is called setup time

when D=0 and clk=0,

input D is reflected at node z, so it take some time to reach the node z via path D-W-X-Y-Z.

The time that data D take to reach at node Z is called setup time

this defines the reason for the setup time within a flip flop.

so, it is necessary that data must be stable before the active edge of clock with delay value of the D to Z node of the latch unit of flip flop and this delay define the setup time of the register

Note:

when the clock =0 , LHS part of the flop is active and RHS part is inactive due to clock is inverted in the RHS region

same, for when clock =1, LHS part of the flop is inactive and RHS part is active, and reflect the result of D input.

Fig: see the where is setup time came

Why Hold time came into picture?

here, flop is made of two latch unit with working in master and slave logic working fashion

so we can assume the LHS part is as Latch-1 and RHS part is as Latch-2

see fig carefully

Now, for working clk will always in invert in nature, so

when latch-1 is active than latch -2 is inactive

when latch-2 is active than latch-1 is inactive

here, hold time came into picture

Time taken by the latch to come into active mode from inactive mode called hold time.

form this switching hold time came

or

we can also understand by this way that

there is the finite delay between the clk and clkbar, so transmission gate some time to switch on and off.

In meantime it is necessary to maintain a stable value at the input to ensure a stable value at node W, which in turn translates to the output, that defining the reason for the hold time within a flop.

there may be combo logic sitting before the first transmission gate ( here you can see the inverter before the transmission gate at the input path from D to W). This introduces a certain delay in the path of input data D to reach the transmission gate. this delay establishes whether the hold time is positive, negative or zero.

Now this relationship between the Combo logic delay and time taken for transmission gate to switch On and Off after clk and clkbar is given. that relationship between that rise to various types of hold time that exist, it can be +ve,-ve or zero hold time.

here, Tcombo define the delay before first transmission gate

Tx define the time taken for transmission gate to switch on and off

CLK represents the clock with an active rising edge

D1, D2 and D3 represent various data signals

S represents the setup margin

H1, H2, and H3 denotes the respective hold margins

Fig: Hold time due to Tx and Tcombo