Find flops that are placed close together and have the same clock and replaces them with Dual or multi-bit flops

CONCEPT

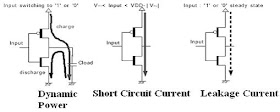

A 1-bit flip-flop has two latches (Master latch and slave latch). The latches need “Ck” and “Ck’ ” signal to perform operations.

In order to have better delay from Ck-> Q, we will regenerate “Ck” from “Ck'”.

Hence we will have two inverters in the clock path.

Each 1-bit flip-flop contains two inverters, master-latch and slave-latch.Merging single-bit flip-flops into one multi-bit flip-flop can avoid duplicate inverters, and lower the total clock dynamic power consumption.

REQUIREMENT

The single-bit flip-flops we want to replace with multi-bit flip-flop must have same clock and set/reset condition.

STEPS TO FOLLOW

Below are few steps can follow or can make a script if want to use in design.

1)Find the flops that can be considered for replacing

For example, all instances of following lib cells only can use for replacing.

{cell name : 1_bit_dff}

find for all the cells and than add them in array with name flops_for_mbit

2)Take first flop (lets name X) from array flops_for_mbit to Check nearby flops to combine.

(a)first get x and y coordinate of first flop

(b)get Net driving to clk pin of that flop.

(c)find nearest instances to that flop with some (for eg 5 micron) spacing in all sides(left,right,bottom,top)

ex. locx->30 and locy ->70

-> give the address of all inst in [25 65 35 75 ] dimesion and sort them

After finding the flops in above dimension first,

->exclude near inst if same inst (X).

->exclude near inst if same inst (X).

->exclude inst if not in flop_for_mbit array.

(d)Lets we found 2 near flops(lets name A,B) so we will take first near flop (start with A)

and check net driving to clk and reset pin of that flop.

(i)Now check to make sure that clocks(*/CK net)) and (*/RESET net) are same of first

near inst A with first flop X.

(ii) get distance from first flop X to first near flop A.

(e)Sort both near instances (A and B) according to their distance from X in increasing

order, we can give it a name as sorted_flops.

(f)Now combine the closest instances into an mbit flop

(i)find clk net,scan net of X flop CK,SCAN &RESET pins which can be use for mbit flop

later so we will not take separate CK,SCAN & RESET pin for all flops which are using

in 1-bit flop.

(ii)set cell Name but need to check with library team that what should be the flop for

Multi Bit .

lets we want to make 2-bit flop and it cell can be like lvt_2_bit_flop.

(iii)set instname to new mbit flop for example MULTI_BIT_FLOP_0

(iv)attach CK,SCAN and RESET net to MULTI_BIT_FLOP_0 instance CK ,SCAN and RESET pin.

(v)Now List all inst X to B first X and other according to sorted_flops.

->Take first flop X take its D pin and Q pin net name(lets DN and QN) and attach

with MULTI_BIT_FLOP_0 inst.

Since we want to use 2-bit flop As we need only 2 bit so we can give D as D0 and

for next nearby inst it will be D1 and same for Q.

->Also take x,y coordinate of X flop which we add with all near flops x and y

coordinate and do avarege to get x,y coordinate of MULTI_BIT_FLOP_0.

->Delete X flop as its added in MULTI_BIT_FLOP _0 as not needed now.

(vi) Now since total near flops are 2(A,B) and after adding our main flop(X) total 3 flops

but we need only two flops for 2-bit MBIT_FLOP so stop after count reach to 2 it can

be (X,A) OR (X,B).

Lets for example all flops which combine to make MBIT_FLOP_0 are (X,A).

So in the end INSTANCE MULTI_BIT_FLOP_0 WITH PINS CK,SCAN,RESET,DO,D1,Q0,Q1 and their respective nets attached with them also its coordinate will be x= (x(X)+x(A))/ 2) and y = (y(X) + y(A))/2

For example,

X, (x,y) = 2,7

A, (x,y) = 2,8

Coordinate of MULTI_BIT_FLOP_0, (x,y) = (4/2, 15/2) = (2,7.5)

3)Revise step 2 for all remaining flops in flop_for_mbit array also next flop instance name will change to MULTI_BIT_FLOP_1 and continuous changing till last flop,

Note : We are deleting flop once its used in MULTI_BIT_FLOP so it will not come in use for other MULTI_BIT_FLOP.

ADVANTAGES OF MBIT FLOPS:

1)Decrease total density of design and delay due to shared transistor.

2)Reduce total clock dynamic power consumption as less number of inverter or by avoiding duplicate inverter.

3)Also decrease number of hold buffer use for design.

4)Reduce clock skew in sequential gates.

DISADVANTAGES OF MBIT FLOPS;

Congestion can degrade as more pins on mbit flops which later increase shorts and drcs in design.